Chiplets Make Case for More Apps

AI, high-end computing, and even consumer applications will require the scalability and flexibility of chiplets to meet future packaging needs.

At a Glance

- Demanding compute requirements are outpacing the ability of system-on-chip packaging to keep up.

- Some consumer apps such as AR/VR now require approaches such as chiplets.

Many chiplet packaging discussions have focused on applications in high-end computing where high density and low latency are needed. But the flexibility and other advantages chiplets offer are also of appeal to makers of complex consumer products, such as AR/VR headsets.

At the recent DesignCon show in Santa Clara, these issues came front and center during a panel session titled, “Chiplets in consumer electronics and infrastructure.” What immediately became obvious was that existing silicon-on-chip technology could no longer scale in a cost-efficient manner for consumer electronics.

“Moore’s Law is no longer applicable,” said Venkat Satagopan, senior signal integrity enginer for Nvidia. “It is more expensive to manufacture silicon-on-chip packages in this manner. In fact, there’s been a 3x increase in semiconductor chip costs, but a 750x increase in compute requirements. This is dictating the need for chiplets and heterogeneous integration.”

Sunil Gupta, a technical lead in Silicon Packaging for Chiplets R&D at Meta, said “AR/VR glasses have immense compute requirements,” he said. Gupta cited developmental work Meta has done on using chiplet technology to develop AR/VR glasses. “The form factor is driving chiplet use.”

Scaling Does Not Work

John Park, Product Management Group Director of EDA Tools and Packaging Technologies for Cadence, also cited the drawbacks of traditional system-on-chip solutions. “Analog RF and I/O does not scale well so Moore’s Law and the latest nodes do not work. Also, with the dependence on memory, memory bandwidth needs to reduce latency, leading to more stacking of memory.”

For an EDA provider, chiplets are leading to a rethinking of design and analysis flow, according to Park. “There is a merging of system analysis, with extremely complex design flows. Signal integrity becomes important. We have moved analysis up front as well as thermal requirements.”

The panel session also explored the software implications of chiplets. Nuwan Jayasena, Fellow at AMD, notes that software release cycles are now in weeks rather than months. “Chiplets make it possible to partition hardware to overcome issues such as non-uniformity,” he said.

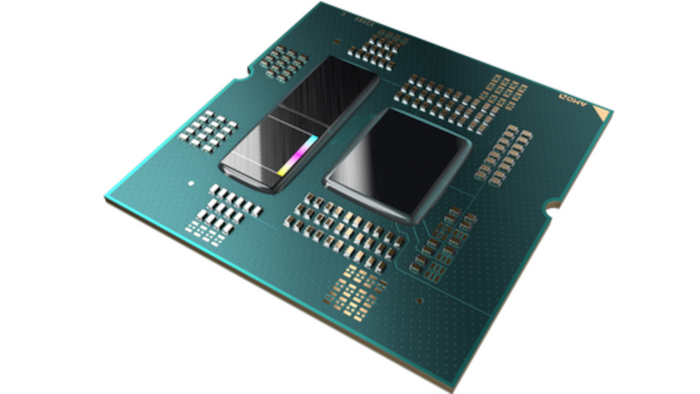

AMD has been utilizing chiplet designs in several of its processors, according to Jayasena, such as the EPYC series and the AMD Instinct M1300. Chiplets give design engineers a means to partition a processor by process node or software function, he added.

Like many semiconductor suppliers, AMD has been phasing in chiplets into its processors to meet high-density packaging needs. Shown here is the company’s Ryzen processor. (AMD)

About the Author(s)

You May Also Like