Extending the Reach of an Application Processor Using Customizable Silicon

February 27, 2013

Chip designers must balance many factors when bringing a new application processor to market, including how much memory and which peripherals, interfaces, and hardware-based accelerators to integrate. Each new feature expands the number of applications and markets that can utilize the device. However, every additional feature also increases cost, size, and power consumption, limiting the types of applications to which the processor is suited.

A processor that supports application-specific interfaces and functionality clearly holds a higher value than one that doesn't. The interfaces required for industrial applications, however, can be different than those used in consumer electronics or automotive systems. Certain applications also need specific features. Given the long lead time to design and bring a processor to market, it can be difficult to anticipate which features the market will demand and be willing to pay for. Product requirements can also change over time, and so OEMs need to be able to introduce new features quickly to address new market opportunities. For example, consider the rapid adoption of touchscreen technology in mobile devices. This technology, introduced to smartphones in 2007, took less than 12 months to become standard across the industry. Silicon manufacturers that could not provide this functionality to their customers lost hard-earned market share.

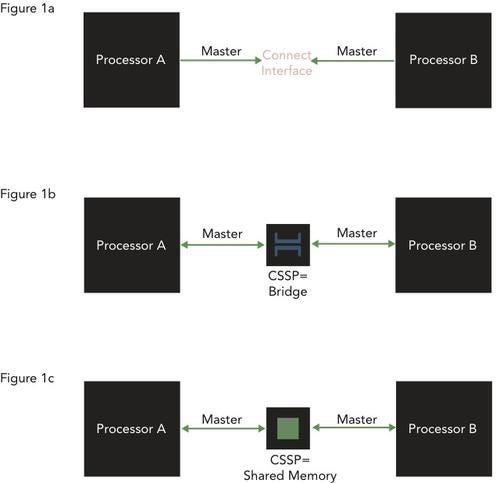

One way to meet the challenge of offering the right mix of standard and application-specific features is to augment an application processor's functionality with a companion device. Rather than increase the cost of a processor across all applications, only those applications that need the added functionality will have to pay for it.

The benefits for silicon vendors to offer a companion device to complement an application processor include:

Test market response to new functionality before committing to investment in an ASIC.

Leverage an existing architecture into new market segments that might not have the volumes to justify spinning a separate processor.

Optimize an architecture for low power and low cost by removing features that can be added back in using a companion chip.

Recover from mistakes in feature specification by being able to make critical features available without delaying release of the application processor.

Enable marketing to continue to provide input late into the design process.

Silicon manufacturers can implement a companion device using a number of technologies. ASIC-based designs, given their heavy upfront investment and long lead time, are really only suitable for implementing commodity features, not for strategically bringing new and product-differentiating features to market. Even ASSPs, with their software configurability, still require OEMs to pre-define exactly the right mix of capabilities to be useful.

Some functionality can be implemented in software. However, such an approach requires substantial processing resources on the application processor. Software offers less performance and increases system cost and power consumption, compared to a hardware-based approach. For some tasks, a hardware approach may be unavoidable.

Functionality can also be implemented in traditional programmable logic. However, SRAM-based logic comes at a high cost and continuously consumes power. SRAM-based programmable logic is also volatile in nature, requiring memory resources to store the FPGA configuration. Hence, the FPGA must be configured at startup. Furthermore, the power consumption of most SRAM-based programmable logic precludes its adoption in mobile applications.

About the Author(s)

You May Also Like