Oversampling Reduces Quantization Errors

July 27, 2012

No matter how many bits an analog-to-digital converter (ADC) provides, the digital output can only approximate the original signal. This approximation gives rise to quantization errors, or quantization "noise." The error values fall between plus or minus 1/2 the voltage represented by the ADC's least-significant bit (LSB) and they have a fairly uniform distribution within this range. Although ADCs with higher resolution reduce the quantization errors, they always remain within plus or minus 1/2 LSB. You can think of the quantization error as adding white noise to the digitized information. By definition, white noise has a "flat" power spectrum over the fsample/2 bandwidth.

So how can a data-acquisition system reduce quantization errors? Because these errors depend only on an ADCs resolution, sampling at a much higher rate than you would normally spreads the quantization noise over a larger bandwidth. And thus the power density for a fixed bandwidth decreases as fsample increases. In practice, a higher sample rate decreases the quantization noise superimposed on the digital data for the signal you want to measure. But the reduction of the noise comes at a price -- more data to process and the need to digitally filter the data. Doubling the sample rate increases the ADC resolution by 1/2 LSB.

This type of oversampling becomes impractical, though, unless you also use a technique called noise shaping. This technique decreases noise in the bandwidth of interest by "shifting" it to higher frequencies where it has less effect on your signals of interest. Sigma-delta, also called delta-sigma, ADCs provide this function and produce high resolutions for relatively low-frequency signals. A sound card, for example, relies on a sigma-delta converter that oversamples at up to 192 ksamples/sec. Some converters operate at 256 times the Nyquist frequency and provide resolutions of 20 or more bits.

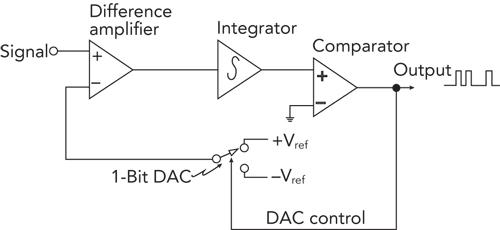

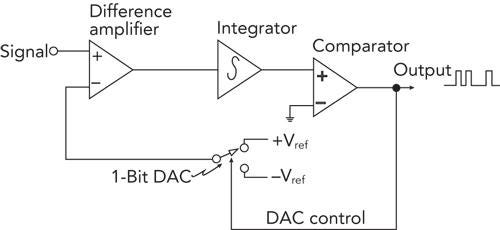

The simplest sigma-delta ADC uses a difference amplifier, an integrator, a comparator, and a 1-bit digital-to-analog converter (DAC), as shown in the figure, in what engineers call a sigma-delta modulator. The DAC provides either a positive or a negative reference voltage and the loop acts to hold the integrator's output at the reference input (ground) at the comparator.

The comparator's output produces logic-1 pulses at a "density" commensurate with the voltage at the signal input. As the voltage increases, the comparator generates more 1s and a decreasing voltage generates more 0s. By summing the error voltage, the integrator acts as a low-pass filter for the input signal and as a high-pass filter for the quantization noise. This in effect "shifts" quantization into higher frequencies. Oversampling does not decrease the total noise power, it simply distributes it at higher frequencies.

Although this type of ADC includes only a 1-bit DAC, it can achieve high resolutions because the modulator output goes through several stages of processing, including decimation, reducing the amount of data to a small fraction of the number of raw samples processed.

Related posts:

About the Author(s)

You May Also Like

.jpg?width=300&auto=webp&quality=80&disable=upscale)