Memory Suppliers Upgrade RAM Performance

Infineon, Rambus unveil new parts as speed and capacity requirements increase.

While product enhancements in the mature memory market tend to take on an evolutionary rather than revolutionary nature, they are nevertheless important for design engineers seeking an edge in processing throughput and signal performance. In recent weeks, Infineon and Rambus have unveiled new memory parts offering improved performance attributes.

Infineon unveiled the third generation of its HyperRam memory, called HyperRAM 3.0. The device features a new,16-bit extended version of the HyperBus™ interface that doubles throughput to 800 MBps. The new parts aim at the mid-level RAM sector for 64 to 512 MB RAM for applications requiring expansion RAM memory, including video buffering, factory automation, Artificial Intelligence of Things (AIoT) and automotive vehicle-to-everything (V2X), according to Bobby John, Senior Manager of Product Marketing for RAM Business of Infineon Technologies.

John explained that HyperRam 3.0 provides higher read/write bandwidth and lower active current than the previous generation of HyperRam and is competitive in performance with parts from other manufacturers. The data rates are equivalent to SDR DRAM, but with much lower pin-count and lower power requirements. The increased per-pin data throughput of the HyperBus interface makes it possible to use microcontrollers (MCUs) with fewer pins and PCBs with fewer layers. This provides opportunities for lower-complexity and thus cost-optimized designs to support target applications.

The part supports the HyperBus/Octal xSPI interface and provides an access time of 35 ns max, data bus width of 16-bit, double data rate (DDR) read-write bandwidth of 800 Mbps. Configurable burst modes include linear burst, wrapped length burst, and hybrid burst.

Infineon’s HyperRAM has a package size of 8 x 8 mm and supports a common footprint with Infineon’s HyperFlash NOR flash memory, using only 12 pins for data transactions.

HyperRAM 3.0 is starting to ship.

DDR5

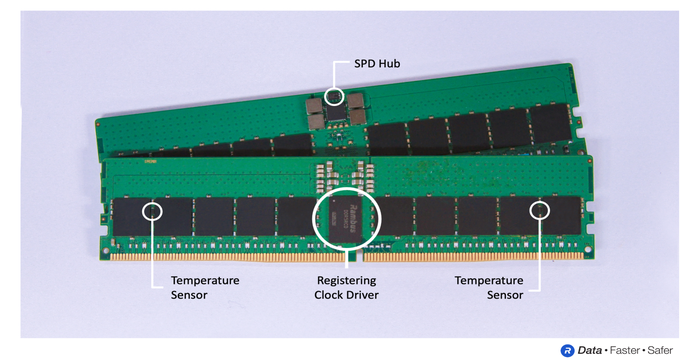

Memory supplier Rambus did not introduce new memory, but recently expanded its portfolio of DDR5 memory interface chips for data centers and PCs. The company unveiled SPD Hub and temperature sensor chips as part of its server and client DDR5 memory module chipsets. Both the SPD Hub and Temperature Sensor are considered critical components on a memory module that sense and report important data for system configuration and thermal management. The parts are designed to complement Rambus’ registering clock driver for DDR5 chipsets.

The parts aim at data-intensive applications such as network storage, network switches, AI and network accelerators, network switches, and server main memory. They enable enhancement system management and thermal control.

Key features of the SPD Hub (SPD5118) include I2C and I3C bus serial interface support, expanded non-volatile memory space for customer-specific applications, and low latency for fast I3C bus rates. Similarly, the TS5110 temperature sensor provides I2C and I3C bus serial interface support, low latency for fast I3C bus rates, and meets or exceeds all JEDEC DDR temperature sensor operational requirements.

Both parts are available now.

Spencer Chin is a Senior Editor for Design News covering the electronics beat. He has many years of experience covering developments in components, semiconductors, subsystems, power, and other facets of electronics from both a business/supply-chain and technology perspective. He can be reached at [email protected].

Spencer Chin is a Senior Editor for Design News covering the electronics beat. He has many years of experience covering developments in components, semiconductors, subsystems, power, and other facets of electronics from both a business/supply-chain and technology perspective. He can be reached at [email protected].

About the Author(s)

You May Also Like

.jpg?width=300&auto=webp&quality=80&disable=upscale)