MathWorks Fleshes Out Its Code Story

July 19, 2012

MathWorks continues to promote automatic code generation as a big differentiator and a key component of its technical computing and simulation story. Officials say its new module allows the 1 million users of its MATLAB tool to generate HDL code with a mere push of the button.

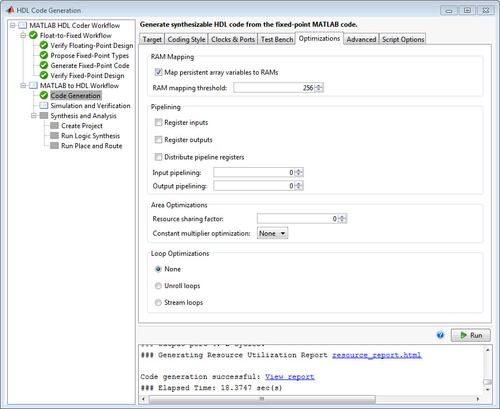

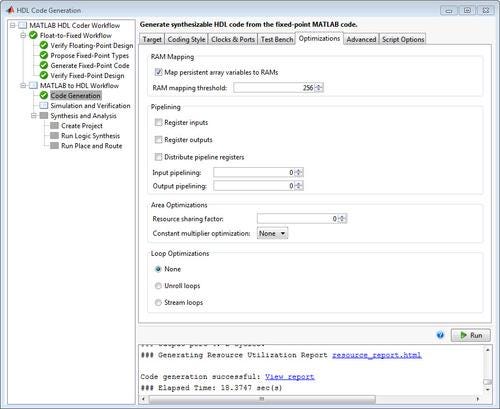

The new HDL Coder product automatically generates HDL code from MATLAB, allowing engineers to implement FPGA and ASIC designs directly from within the MATLAB technical computing language. HDL Coder generates portable, synthesizable VHDL and Verilog code from MATLAB functions and Simulink models (this capability was announced last April), which can now be used for FPGA programming or ASIC prototyping and design.

MathWorks began talking up its code generation capabilities in earnest last April, when it unveiled its MATLAB Coder, a tool that lets design engineers automatically generate readable and portable C or C++ code directly from MATLAB algorithms. With code generation capabilities now for both C and HDL, users no longer have to convert code manually or physically write code -- a process MathWorks officials said is highly iterative and time-consuming and introduces the possibility of design errors, which could ultimately impede time to market.

The company says it has a jump on its competition when it comes to automatic code generation, which is all about helping its customers meet their rigorous product delivery schedules. "It's all about time to market and quality in terms of rigorous verification," Tom Erkkinen, embedded applications manager at MathWorks, told us. "One of the ideal ways to improve time to market is to automatically generate code. If people hand code FPGAs, it could take weeks or months. With this approach, the coding is nearly instantaneous."

Engineers can now spend more time creating designs, Erkkinen said, and once the design is simulated properly, they can push a button to get code that will automatically run on their FPGA. They really get no value from spending time translating between one language (MATLAB or SIMULINK) and another (HDL or C++).

Time to market advantages aside, it's not a slam dunk that users will trust (and embrace) automatic code generation over hand coding. Errkinen said this has been an ongoing hurdle for MathWorks, but it is making progress. Users have been using the automated code for years as part of their rapid prototyping and test procedures, but they have been more hesitant to embrace automated code for production processes, due to concerns about the quality and efficiency of the code. "The question is and has been is the code fast enough and small enough," he said. "It's been an iterative process to improve the efficiency of our code, and it's a never-ending quest. It's been one of our biggest barriers."

Each subsequent code generation release drives home that point a bit further. "Each release is getting better and better, and we're knocking through those doors and making it clear that the tool can achieve a reasonable quality of HDL code."

In addition to HDL Coder, MathWorks announced HDL Verifier, an offering that includes FPGA hardware-in-the-loop capabilities for testing FPGA and ASIC designs.

Related posts:

About the Author(s)

You May Also Like