The FPGA Turns to Optical Interconnects

Semi companies bet on optical connects to solve last-mile chip interconnect issues.

Optical interconnects have been lurking in the background in recent years as potential solutions to the issue of interconnecting hundreds of I/O in dense electronics assemblies as performance and speed requirements increase. Now, with applications such as AI and machine learning increasing, the cry for alternatives to traditional copper interconnects are growing louder.

“The fundamental issue is that more power is required to move data, particularly as AI emerges,” said Terry Thorn, Vice President of Commercial Operations for Ayar Labs, in a recent interview with Design News. Ayar, a startup company founded in 2015, has been working with companies such as Intel to bring optical interconnects to market.

Thorn asserts that can be substantial improvements in computing throughput by replacing traditional copper interconnects with optical ones. The improvements come in the way of increased system bandwidth, lower power consumption, and improved latency.

FPGAs With Optical Ports

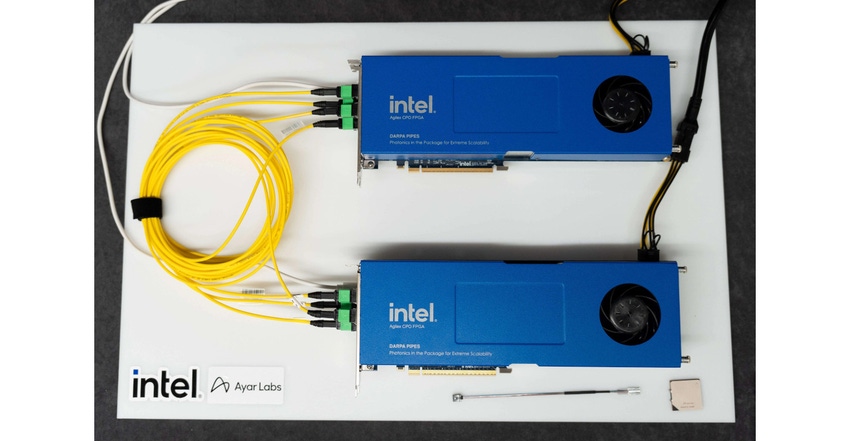

One project Ayar is involved in is an FPGA (Field Programmable Gate Array) being developed with Intel. Ayar initially demonstrated a 4 Terabits per second (Tbps) FPGA at the Optical Fiber Conference back in March. While FPGAs connected to pluggable optics have existed for some time, they traditionally rely on Ethernet, with current pluggable optics typically providing 100- or 400-Gbps speeds. The integration of optics in-package allows make it possible to accelerate performance up to 4-Tbps, and without the Ethernet latency hit.

The companies are leveraging chiplet technology advances for optical-based FPGAs. Intel and Ayar are now demonstrating an optical FPGA consisting of two TeraPHY optical I/O chiplets, each capable of 4 Tbps bi-directional bandwidth. These chiplets are connected to a 10 nm FPGA fabric die — the same core fabric used in Intel Agilex FPGAs. The optical communication is powered by two of Ayar’s SuperNova light source modules, supporting 64 optical channels of high-speed, error-free communication across 8 fibers on each chiplet.

Each TeraPHY chiplet has 8 Tx and 8 Rx communication links, totaling 16 Tx and 16 Rx fibers of communication to and from each interconnected FPGA. The result is a system containing 32 Tx and 32 Rx optical links, with each TeraPHY chiplet capable of sending and receiving 2 Tbps in each direction simultaneously. A video of Ayar and Intel’s work follows below.

The integration work with Intel is demonstrating the potential of chiplet-based architectures to combine chips in different process nodes and technologies from different vendors into a single package. This co-packaged integration development does not require any change to Intel’s FPGA, the core computing component.

The electrical interface between the Intel FPGA and the Ayar Labs’ TeraPHY optical I/O chiplet is AIB (Advanced Interface Bus), a low-power and low-latency wide parallel interface. AIB is a precursor to UCIe™ (Universal Chiplet Interconnect Express), an open industry standard that defines the interconnects between chiplets within a package.

According to Ayar’s Terry Thorn, the FPGA could pave the way to optimize massive computing and AI applications with higher density system architectures. Other potential uses include network edge, radar sensor applications, and telecom system architectures.

Thorn added that besides the FPGA, Ayar is currently working with several other OEMs on designs to demonstrate the feasibility of optical interconnects. He expects commercially available products to use optical interconnects by 2026.

Spencer Chin is a Senior Editor for Design News covering the electronics beat. He has many years of experience covering developments in components, semiconductors, subsystems, power, and other facets of electronics from both a business/supply-chain and technology perspective. He can be reached at [email protected].

About the Author(s)

You May Also Like