IP Subsystems Speed ASIC Design

Specialized IP blocks for power management, sensing, and sleep management ease IP integration and reduce costs.

Integrating analog IP into an ASIC has traditionally been a hit or miss process with engineers with some functions having to be implemented off the chip, making monitoring of some parameters more difficult. Agile Analog, a supplier of customizable analog IP, has launched a range of analog subsystems, covering power management, PVT sensing, and sleep management. According to the company, these subsystems reduce the effort required to integrate multiple analog IPs into any ASIC by allowing the IP to be dropped straight into a digital design flow and connected via a standard peripheral bus, such as AMBA APB.

For design engineers, the analog subsystem can help cut design time and speed time-to-market. The subsystems look just like a normal block of digital IP with the standard interfaces that engineers would expect, making them easy to understand and handle. They to be customized to the customer’s exact requirements.

The subsystems could also help alleviate a shortage of skills expertise in working with analog designs, noted Chris Morrison, Director of Product Marketing at Agile Analog. During a conference call with Design News, Morrison said that many newer product designs abandoned some analog functions due to the problems integrating analog functions into the largely digital designs. The IP subsystems Agile is offering should help alleviate those issues, Morrison noted.

As with all Agile Analog IP, the digitally wrapped subsystems are process and foundry agnostic, and each design is optimized for the customer’s specific PDK. Integrating IP within a subsystem further enhances the customer’s design by removing duplicate analog functions, reducing design rule checking (DRC) requirements, and optimizing interconnects. These lead to increased noise immunity, lower power consumption and smaller area.

Another advantage of the IP blocks is that Agile performs the verification requirements, thus reducing customer design and verification time and lowering the cost of licensing mixed-signal design tools and simplifying integration. Agile Analog’s subsystems are supplied with a full set of supporting collateral, including System Verilog models for easy integration into customers’ existing digital verification flows.

Power Management Subsystem

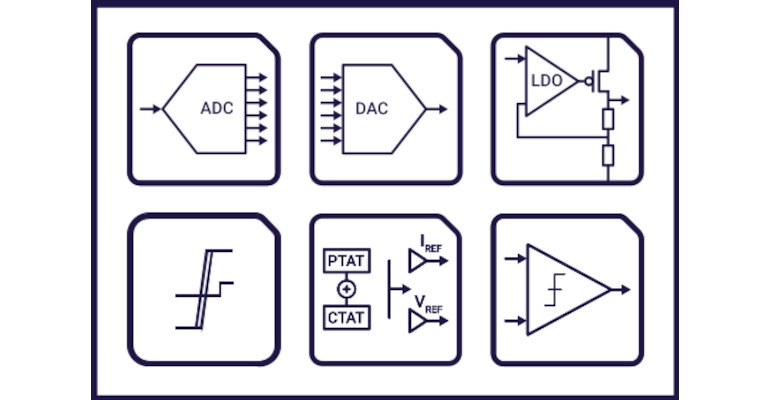

The agilePMU Subsystem is an efficient and highly integrated power management unit for SoCs/ASICs. Featuring a power-on-reset, multiple low drop-out regulators, and an associated reference generator. The agilePMU Subsystem is designed to ensure low power consumption while providing optimal power management capabilities. Equipped with an integrated digital controller, the agilePMU Subsystem offers precise control over start-up and shutdown, supports supply sequencing, and allows for individual programmable output voltage for each LDO.

Sensor Subsystem

The agilePVT Sensor Subsystem is a low power integrated macro consisting of process, voltage, and temperature sensors, and an associated reference generator, for on-chip monitoring of a devices’ physical, environmental, and electrical characteristics. Equipped with an integrated digital controller the agilePVT Subsystem offers precise control over start-up and shutdown. Status monitors provide real-time feedback on the current state of the subsystem, ensuring optimal system performance over the full product lifecycle.

Sleep Management Subsystem

The agileSMU Subsystem is a low power integrated macro consisting of the essential IP blocks required to securely manage waking up a SoC from sleep mode. Typically containing a programmable oscillator for low frequency SoC operation and RTC, a number of low power comparators which can be used to initiate the wake-up sequence, and a power-on-reset which provides a robust, start-up reset to the SoC. Equipped with an integrated digital controller, the agileSMU Subsystem offers precise control over wake-up commands and sequencing.

Agile Analog is initially making the subsystems available to its ASIC customers. Agile Analog has also become a member of the TSMC IP Alliance Program, a key component of the TSMC Open Innovation Platform® (OIP). The complete range of Agile Analog’s innovative analog IP is now available to TSMC customers, covering data conversion, power management, security, IC monitoring, and always-on-domains.

Spencer Chin is a Senior Editor for Design News covering the electronics beat. He has many years of experience covering developments in components, semiconductors, subsystems, power, and other facets of electronics from both a business/supply-chain and technology perspective. He can be reached at [email protected].

About the Author(s)

You May Also Like