When All CPUs Are the Same, How Will You Pick Your MCU?

It’s no secret that more and more microcontrollers are using ARM CPUs.

November 9, 2015

It’s no secret that more and more microcontrollers are using ARM CPUs. There are surely some variations among the different CPUs offered by ARM; in fact, several months back I lectured a Design News Continuing Education Center (CEC) course, sponsored by Digi-Key, on the ARM Cortex-M4, and there are several other ARM CPU-related courses in the CEC archive. This brings up an interesting question: When the CPU is the same between different microcontrollers, what criteria do you use to decide on one versus others? If you have wondered about this before, you are in luck.I will lecture another Design News CEC course, Compare and Contrast Different Makes of Microcontroller Peripherals, Nov. 16-20, that will discuss this exact topic. I will cover the similarities and differences between the various peripherals on many common MCU families available on the market. As the CPUs have become similar, the peripherals added to these CPUs have become much different across different MCU families. In fact, MCU peripherals have become very different.

On the surface, many peripherals implement industry-standard functions, like USB, UARTs, SPI, I2C, and Ethernet, so how different could these implementations be? Well, it turns out that implementations for these standard functions can be dramatically different. One example is the venerable SPI (serial peripheral interface) function, a fairly simple interface that uses just four wires to connect peripheral devices to an MCU. The protocol is well defined, and even the timing is standard. What could an MCU manufacturer do differently?

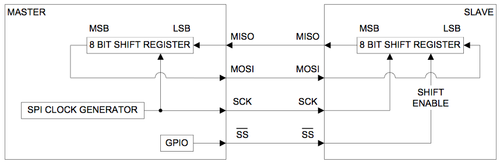

If you look closely at a few different SPI peripheral implementations, you soon discover that there can be significant differences. Sure, all SPI implementations start out by supporting the key elements of the standard. Figure 1 shows the core of an SPI implementation: a master that controls the interface and some number of slaves that act as the peripherals, of which each uses an 8-bit shift register to send or receive data over the MISO and MOSI signals.

The master supplies the system clock (SCK), which controls shifting. A slave select signal (SS) identifies which slave is being addressed by the master, and this can be replicated as needed to support multiple slave devices.

Figure 1: SPI implementation block diagram.

(Source: Atmel Corp.)

It would seem that there is little latitude for different implementations, but there is actually quite a range of implementations. One of the first differences when implementing standards is which version of the standard to support.

For example, QSPI, the newer version of SPI, allows for much faster data transfers by using four pins to transfer information instead of one. This can be very important for higher performance systems and when a QSPI memory is particularly used to boot or configure the MCU. Another variation is the data length transferred. The version shown in Figure 1 supports 8 bits, but lengths of 16 bits and 32 bits are possible. Longer data lengths can be important when interfacing with memories, analog-to-digital converters, and LCD controllers, for example.

Interrupt support can also be a key difference. If interrupt support provides just a single interrupt, you may not know if it is for a transmission, a reception, or an error. It can take critical clock cycles in the interrupt service routine to figure out how to service the interrupt. If the SPI peripheral can issue a different interrupt for each type of request, the interrupt service routine can respond more quickly, since it automatically “knows” the source of the request.

READ MORE BLOGS BY WARREN MILLER:

Some SPI peripherals may support the use of on-chip direct memory access (DMA). This feature allows data to be transferred without CPU support, freeing up the CPU to do other tasks or, perhaps more important, transfer to a low-power state until the CPU is needed for computation or decision-making. SPI peripherals may also provide a separate baud rate generator so that data transfer speeds can be adjusted independently of peripheral and clock speeds.

When interfacing to some MCUs, supporting an execute-in-place (XIP) capability can be critical. With XIP, code can be executed directly from an SPI flash memory -- often an important capability during the boot process. Along with XIP, supporting address modes of up to 32 bits can be important for large memories, over 128 Mbit.

I hope that this elucidates some of the differences that even the simplest MCU peripheral can present and has you interested in learning more. Sign up for my Nov. 16-20 Design News CEC online course, Compare and Contrast Different Makes of Microcontroller Peripherals. All Design News CEC courses are archived, so check out my series on the ARM Cortex-M4, as well as several other ARM CPU-related courses in the CEC archive. I hope to see you there.

Warren Miller has more than 30 years of experience in electronics and has held a variety of positions in engineering, applications, strategic marketing, and product planning with large electronics companies like Advanced Micro Devices, Actel, and Avnet, as well as with a variety of smaller startups. He has in-depth experience of programmable devices (PLDs, FPGAs, MCUs, and ASICs) in industrial, networking, and consumer applications and holds several device patents.

Like reading Design News? Then have our content delivered to your inbox every day by registering with DesignNews.com and signing up for Design News Daily plus our other e-newsletters. Register here!

Design News will be in Orlando in November! Design & Manufacturing South will be in Orlando Nov. 18-19. Get up close with the latest design and manufacturing technologies, meet qualified suppliers for your applications, and expand your network. Learn from experts at educational conferences and specialty events. Register today for our premier industry showcase in Orlando.

About the Author(s)

You May Also Like