More On Sigma-Delta ADCs

August 1, 2012

A previous column, Oversampling Reduces Quantization Errors, included a diagram for, and a short description of, a single-stage sigma-delta analog-to-digital converter (ADC). The ADC produced a stream of logic-1 and -0 pulses that represent the digitized analog input. Analog Devices has an online demonstration that shows how a sigma-delta ADC works so you can watch values change step-by-step.

Keep in mind that the ratio of logic-1 to logic-0 bits indicates the value of the unknown input signal. If you have a converter with a 0-to-5-volt input range and apply 4.2 volts to its input, over a short time you will obtain a bit stream such as:

...0111111111111011111111111101111...

The ratio in this small sample amounts to 12/13 or 0.923, or 4.6 volts. Over time, though, the ratio would come to 0.84. Likewise, a 4.5 volt input would create a string of bits similar to:

...111011111111111111111110111...

So you have a higher ratio of 1s to 0s. Again, the average would settle at 0.900. The number of bits in these examples has no direct relationship to the number of bits in the ADC's digital output.

The string of 1s and 0s goes to a circuit that averages the information over time in a digital low-pass filter and also decimates the data so you obtain results at a rate lower than the sample rate. Filtering and decimation go beyond this discussion. (See: Improving ADC Resolution by Oversampling and Averaging and Principles of Sigma-Delta Modulation for Analog-to-Digital Converters.)

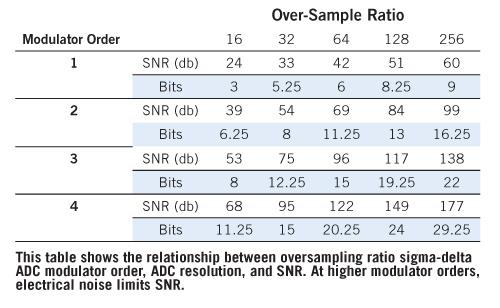

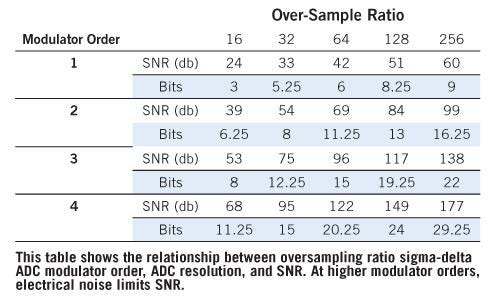

Chip designers further improve ADC signal-to-noise ratios (SNRs) by using second- and third-order modulators that include additional summing amplifiers and integrators. You buy these converters, you don't have to design them. You can dig deeper into the theory and math if you wish. The table nearby shows improvements in SNR and resolution calculated for first- through fourth-order sigma-delta ADCs. The over-sampling ratio represents fsample/2*fbandwidth. These values reflect only quantization noise and do not account for other noise sources.

A real ADC, such as the Analog Devices AD7190 ADC, operates with signals from sensors and transducers from a few Hertz to 2.4kHz, and delivers 24-bit data with no missing codes. This ADC offers 22.50-bit noise-free resolution for a 5V input signal.

Because sigma-delta ADCs have such a high sample rate, often they need only a simple R-C anti-alias filter on an analog input. A reader recently asked if I would cover anti-alias filters in more detail, which I will in the next column.

Reference:

Van Ess, Dave, Signals from Noise: Calculating Delta-Sigma SNRs.

Related posts:

About the Author(s)

You May Also Like

.jpg?width=300&auto=webp&quality=80&disable=upscale)