Create Once and Test Everywhere: The Promise of Portable Stimulus

What is Portable Stimulus and how will it help IP and full chip verification across platforms including simulation, emulation and prototyping?

March 20, 2020

The problem was straightforward: Different test platforms were used by different engineering professionals throughout the verification phases of simulation, emulation, prototyping and other types of testing. In the semiconductor chip world, verification refers to the process in which a design is tested (or verified) against a given design specification before tape-out, i.e., before the design is made into a silicon chip.

The solution seemed straightforward: Create a high-level test environment which could be reused on these different platforms and at different times throughout the verification process.

The reality was anything but straightforward. First of all, each verification activity had to satisfy a different set of requirements. Further, each verification platform used different languages and approaches specific to the aspect of the system that were being are trying tested. It wasn’t easy to reuse verification requirements from one platform to another.

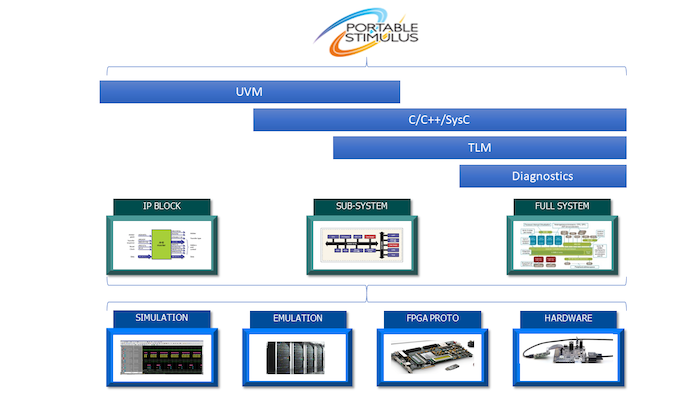

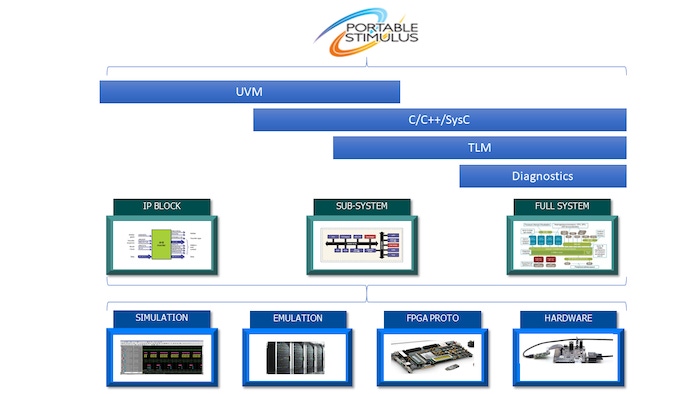

That’s why the Accellera Portable Stimulus Standard (PSS) was developed back in 2017. The standard’s purpose was to specify the test intent in an abstract way that could be mapped to different requirements on different platforms. Thus, a single specification could be developed into test suites and then used by many different people and deployed to many different environments. In this way, hardware chip designers through embedded software programmers could deploy test and verification suites across many different test environments.

Today, many chip developers rely on SystemVerilog to do both design and verification of chip systems. Formally, SystemVerilog is both a textual hardware description language (HDL) and a hardware verification language (HDL).

And therein was the challenge. SystemVerilog is great as a language used to create hardware checkers and testbenches. But it is not well suited to reuse the stimulus code at the software system level. At this high level of abstraction, tests are generally executed on embedded processors inside the design where machine code or C-code instructions have access to operating system services.

To help address these hardware and software coding differences, the Accellera standard defined two languages for creating portable stimulus. One is a custom domain-specific language (DSL) that uses a structure not dissimilar to that of Python. The other is a class library for C++ that allows a use more familiar to software developers – a similar approach to that used for SystemC.

“Portable Stimulus allows for reuse across various platforms and across chip hierarchy,” explains Lu Dai, Chairman of Accellera. “An SoC design can write a test using PS which, through a tool flow, will generate the C language-based test. That native test can then be reused from pre-Silicon verification to emulation and even to post-Silicon software bring-up.

Dai went on to say that reuse across the hierarchy – from IP blocks to the full SOC verification – was more challenging because tool vendors don’t yet easily support that tool flow.

The latest version of the Portable Stimuls Standard (PSS) was the subject of much discussion at the recent Design-Verification Conference (DVCon) 2020. Among other things, it was announcement that the next version, PSS 1.1, would available for public review by the second half of 2020. This version will include modeling improvements, better test realization and enhancements for the verification programmer.

|

Image Source: Accellera |

RELATED ARTICLES:

John Blyler is a Design News senior editor, covering the electronics and advanced manufacturing spaces. With a BS in Engineering Physics and an MS in Electrical Engineering, he has years of hardware-software-network systems experience as an editor and engineer within the advanced manufacturing, IoT and semiconductor industries. John has co-authored books related to system engineering and electronics for IEEE, Wiley, and Elsevier.

About the Author(s)

You May Also Like