Is RISC-V Processor Hardware or Software?

Some professionals still misunderstand if RISC-V refers to processor hardware and software, and whether it's free or not.

September 30, 2020

RISC-V technology is used in the development of chip hardware, software, and the creation of intellectual property (IP). Recently, the open standard has gained increased interest with the potential US-based Nvidia acquisition of UK-based Arm processor systems. Arm processors dominate the global embedded and chip IP markets.

Many have noted that the acquisition by Nvidia will spur the growth of RISC-V technology as current Arm customers may now see NVidia as either a direct competitor or at least a quasi-competitor. For example, Chinese companies including Alibaba and Huawei - members of the open-source RISC-V foundation - may be one of the many potential beneficiaries of any retreat from Arm processor technology.

But many electronics developers and related professionals still don’t fully understand the basics of the RISC platform or how it can help them. Perhaps that’s why more than one keynote at the RISC-V Global Forum focused on defining what is meant by RISC-V technology. The following slides highlight the fundamental hardware and software concepts and values of the tech.

RISC-V Basics

The first RISC-V Global Forum (virtual) provided a variety of keynotes focused on Asian, European, and US development of this free and open technology. The forum was sponsored by RISC-V International, a global nonprofit association founded in 2015. According to the association, “RISC-V brings a new era to processor innovation through open standard collaboration.” During his “State of the Union” keynote, Krste Asanovic, Chairman of the board of the RISC-V International, added more details to this description.

Asanovic started by looking at where RISC-V is now. Today, the RISC-V instruction set architecture (ISA) is seen as a real alternative to existing proprietary ISAs. However, it wasn’t that long ago when the processor community doubted that an open standard for the ISA was even possible. Now, RISC-V has been widely adopted.

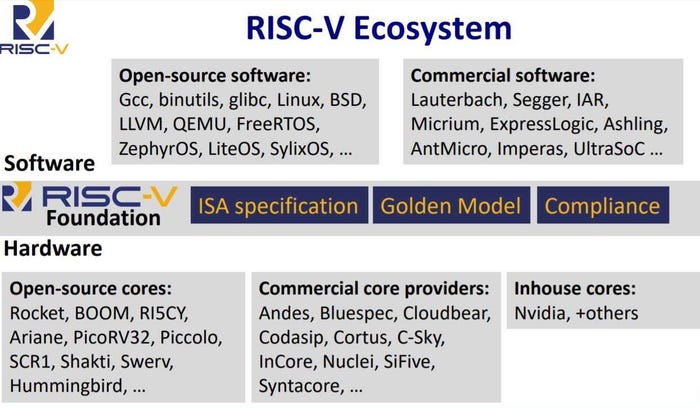

To understand RISC-V, one must really understand the ecosystem. Asanovic explained that the ISA specification, model, and compliance testing, managed by RISC-V International, really sits in the middle of the ecosystem. The spec is really the bridge between the many hardware implementers, that use the spec to build their electronic and embedded designs.

One thing people often mistake about RISC-V is that they believe it refers to an open-source hardware processor. This is an understandable but incorrect assumption.

“RISC-V is an open specification and because the spec is open, it means you can have open-source processors,” explained Asanovic. “There's a big variety of those available from different places, all around the world, developing opensource cores. But in addition to open-source cores, there are also commercially licensed cores.” This can get a bit confusing, as some open-source software can also be commercial. But commercial typically refers to "proprietary” systems.

Further, developers usually must pay for commercially available cores, but the companies that sell them also verify and support the cores. In addition to opensource cores and commercial cores, there are also cores developed in-house. For example, Nvidia develops its own RISC-V cores for its GPUs. So, on the hardware side, users can choose whether they want an open-source implementation, a commercial implementation, or just build their own.

On the software ecosystem side, RISC-V supported in the open-source domain like GCC and Linux. However, there is a large commercial software ecosystem being developed around RISC-V. The great thing about RISC-V is that it acts as an intermediate open specification. This means that, as long as the hardware processor developers follow the spec, then they can take advantage of the large software ecosystem, noted Asanovic. Similarly, the software developers understand that their tools will work across all the hybrid implementations from many different vendors.

|

RISC-V ecosystem. |

ISA?

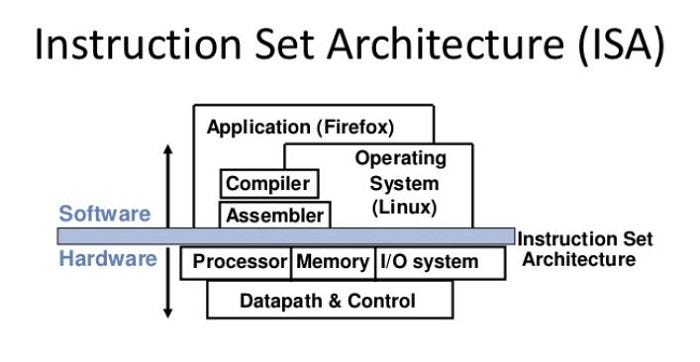

Before going on, let’s make sure that everyone understands what ISA means. RISC-V is a free, open-source instruction set architecture (ISA) that is based on reduced instruction set computer (RISC) principles. That’s why it’s incorrect to say that RISC-V is a hardware processor.

Specifically, an ISA is an abstracted model of a computer. A processor is an implementation of an ISA. It is the part of the processor that is visible to the programmer or compiler writer. An ISA is analogous to a human language but instead of communication from person to person, the ISA enables the communication between the hardware and software of a processor.

The ISA represents the primitive operations of the processing machine that are available for use by assembly programmers and compiler writers. One of the main functions of a compiler is to allow a programmer to write an algorithm in a high-level language without having to care about CPU-specific instructions.

Each processor has its own ISA, be it from ARM, Intel, AMD, Nvidia, etc. However, unlike the proprietary ISAs for these commercial processors, anyone can use the open-source RISC-V ISA for free. They can use it as the basis for their own processor implementation, rather than pay fees for the commercial processors. In other words, anyone can use the RISC-V ISA to make in-house processor implementations to sell as an off-the-shelf physical device or license as IP cores that can be used in the SoC designs of others.

|

Instruction Set Architecture (ISA) block diagram. |

The Future

Asanovic concluded his keynote by focusing on future goals for RISC-V. One of the primary goals is to run all software. Developers, companies, and the open-source communities are investing a great deal in the RISC-V architecture, so it must be stable to continue to run without surprises. It’s difficult to run existing software or develop new ones if the basic software is unstable. Finally, supporting innovation is critical.

In addition to stability, RISC-V must be feature complete. At the least, this requires includes of a hypervisor, security features, functional safety, support for high-performance computing, trace and debug extension, RAS features better code size, and more. Adding these features must be done with care, as it's difficult to retain stability and coherent ISA design if too many new features are added simultaneously.

Finally, to grow and prosper, RISC-V must continue to support innovation. The original, modular ISA design allows standard software to run despite the existence of custom instructions. This approach enables developers to innovate with compatibility and stability, said Asanovic. The beauty of an open specification means that no permission is needed to experiment and use and publish the results. The allocation of the RISC-V standardization effort relies on members' needs and not simply adding the latest technology for the sake of technology.

John Blyler is a Design News senior editor, covering the electronics and advanced manufacturing spaces. With a BS in Engineering Physics and an MS in Electrical Engineering, he has years of hardware-software-network systems experience as an editor and engineer within the advanced manufacturing, IoT and semiconductor industries. John has co-authored books related to system engineering and electronics for IEEE, Wiley, and Elsevier.

About the Author(s)

You May Also Like