Here’s Why Intel Was So Smart to Snap Up Altera

July 13, 2015

Now that we have had some time to digest the move by Intel to acquire Altera, perhaps the smart ideas that can develop from the combined company are a bit clearer. Altera is one of the leaders in programmable logic technology, and it's clear that this pervasive technology will continue to find its way into the heart of just about every electronics product. You are always going to need to add a new feature, glue a few interfaces together, or add some custom logic to differentiate your design from your competitor.

The big ideas to spin out of the Altera programmable logic technology, once Intel applies its keen knowledge of the broad computing marketplace to the new entity, will be big steps up from glue logic applications. In fact, it might be better described as glue processing.

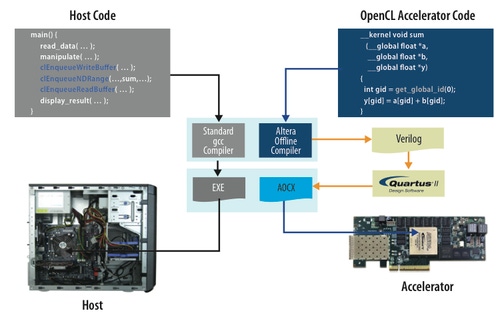

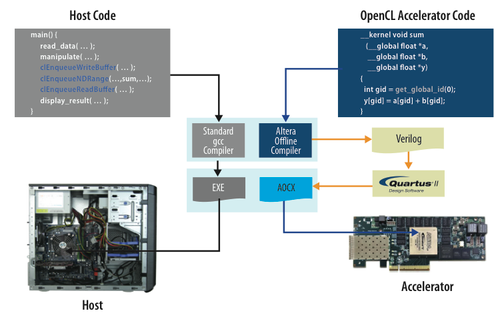

What programmable logic promises over the next few years is a radically different approach to processing data by "gluing" together radically different hardware elements in order to do it more efficiently. One example of this approach is already available to target SoC FPGAs -- those with both a dedicated CPU and on-chip programmable fabric -- in the form of OpenCL, as illustrated in Figure 1.

On these devices, host code can run on a CPU, with hardware-accelerated code running on the FPGA on the peripheral board. All the user of the host computer knows is that the data is being processed much faster. Now, consider that the CPU and the FPGA can be on the same chip. Code runs on the CPU and can be accelerated by on-chip hardware that is all "glued" together by the FPGA fabric.

Altera describes OpenCL in this way: "The Altera SDK for OpenCL allows the user to abstract away the traditional hardware FPGA development flow to bring the inherently parallel and flexible architecture of the FPGA to the software developer with a much faster and higher level software development flow." Well, this sounds pretty good, and it looks like Altera has found a way to make it easy for software developers to reap the benefits of programmable logic without needing to do any hardware design. Cool.

As they say on TV, however, "But wait, there's more." Not only can OpenCL map code into FPGA hardware to accelerate processing, it can target CPUs, DSP blocks, GPUs, and, in the broadest case, any "speed-up" hardware you can design (with some additional work from OpenCL, of course). Want to speed up your vision processing algorithm? No problem; just select a device with some hardware to accelerate your algorithm and let OpenCL do the mapping. Not fast enough? Target more acceleration hardware -- after all, FPGAs are good at connecting parallel hardware together.

MORE FROM DESIGN NEWS: Low-Power FPGAs: Just Like Jumbo Shrimp?

Now you can probably see where this could take things. It seemed like we were hitting a wall with single chips that have multiple homogeneous CPU cores. It's tough to get the right code and data to the right processor and manage the various caches, intermediate memories, and intermediate buffers. With the OpenCL approach and massive heterogeneous processing capability on a single chip that automatically matches the data and the algorithm with the optimal hardware, efficiency can skyrocket. You do pay a penalty to use programmable logic -- it takes more transistors than "hardened" processing blocks -- but programmable logic is a great way to find out what algorithms are popular so you can add new fixed hardware elements (DSP blocks, CPUs, and GPUs are just the starting point) that benefit key applications. Who better than Intel to figure out what "speed-up" hardware is going to be popular and create targeted devices for the most popular applications.

If you are interested in learning more about the current state-of-the-art in SoC FPGAs, consider attending my next Design News Continuing Education Center (CEC) online course, "Hands-On SoC FPGA Design," sponsored by Digi-Key. You will be able to follow along and see several example designs that show the potential for this new mix of CPU and FPGA data processing. You can even target a development board if you want to really get your hands dirty.

The kit I'm targeting for my five-day course is the Digilent Zybo Development Kit for the Xilinx Zynq-7000, available from Digi-Key. Attend the course and see for yourself just how smart Intel is to get access to Altera's amazing technology.

Warren Miller has more than 30 years of experience in electronics and has held a variety of positions in engineering, applications, strategic marketing, and product planning with large electronics companies like Advanced Micro Devices, Actel, and Avnet, as well as with a variety of smaller startups. He has in-depth experience of programmable devices (PLDs, FPGAs, MCUs, and ASICs) in industrial, networking, and consumer applications and holds several device patents.

About the Author(s)

You May Also Like