IP tool reduces design iterations for silicon on-chip parts, overcoming the delays imposed by pipeline insertions as circuits get more complex.

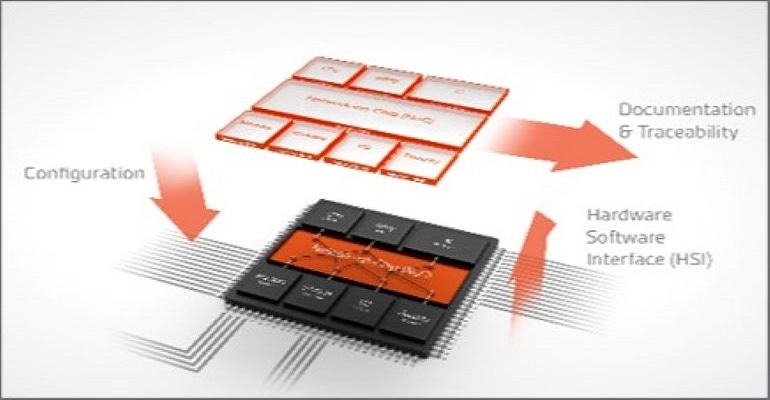

As with other designs, engineers looking to create system-on-chips are seeking to accelerate the design process. Arteris, Inc., a provider of system IP, has launched its Arteris FlexNoC 5 physically aware network-on-chip (NoC) interconnect IP. FlexNoC 5 enables SoC architecture teams, logic designers and integrators to incorporate physical constraint management across power, performance and area (PPA) to deliver a physically aware IP connecting the SoC.

According to Arteris, this technology enables five times faster physical convergence over manual refinements with fewer iterations from the layout team for automotive, communications, consumer electronics, enterprise computing, and industrial applications.

“Circuit complexity continues to get more complex,” said Michal Siwinski, CMO at Arteris, during a recent interview with Design News. “There are more transistors and more logical cores. Power, performance, and area have become issues. Also, market pressures are putting the squeeze on market realities.”

Design engineers have had to deal with manual workflows that typically include numerous iterations of pipeline insertions, creating constraints for physical placement of units, and lengthy network on-chip placement plus route iterations to converge on the SoC PPA targets.

SoCs contain multiple NoCs, accounting for 10 to 12% of silicon. The physical effects are even more pronounced at advanced nodes of 7, 5, and 3 nm.

Speeding Place and Routing

FlexNoC 5 physical awareness eliminates these iterations and shortens the duration of various manual steps. It gives place-and-route tools a better starting point. It shrinks interconnect area by 15% or more and reduces NoC IP power due to less pipeline logic and fewer LVT cells. The resulting physically optimized NoC IP instance is then ready for output to physical synthesis and place and route for implementation.

For Arteris, the interconnect IP has a captive market. The IP from the NoC (network on-chip) interconnect provider has been designed into over 3 billion SoCs. According to Arteris, the company has a majority share of the automotive ADAS SoC market,and is compatible with EDA software and foundry processes.

The IP expands support for Arm AMBA 5 protocols and IEEE 1685 IP-XACT, including a connectivity flow with Arteris Magillem for NoC integration with other SoC IP blocks. FlexNoC 5 also supports the Arteris resilience option for automotive functional safety qualification and data center reliability, the advanced memory option for optimizing memory traffic, and the Arteris option for very large designs.

Arteris is now sampling FlexNoC5 with selected customers, with wider availability expected later this year.

Spencer Chin is a Senior Editor for Design News covering the electronics beat. He has many years of experience covering developments in components, semiconductors, subsystems, power, and other facets of electronics from both a business/supply-chain and technology perspective. He can be reached at [email protected].

About the Author(s)

You May Also Like