Tensilica DSP cores aims at radar apps requiring sensor fusion, such as LiDAR, robots.

Cadence is probably best known for its EDA software, but the company has also offered semiconductor IP for a number of years. In an effort to capture more applications in compute-intensive applications in radar and LiDAR, the company has expanded its Tensilica ConnX DSP portfolio with two new versions that support multiple data types and requirements for higher data rates, lower latency, and larger dynamic range.

While Cadence has long offered DSP cores for a wide range of applications including traditional radar, the new cores target include radar systems for gesture recognition, sensing, and surveillance. Sensors are a prime use case, noted David Bell, Tensilica DSP and AI Product Marketing Manager for Cadence, in a recent interview with Design News. “Lots of sensors have been added to vehicles, robots, IoT devices. The multiple sensors require sensor fusion, which in turn requires heavy floating-point and linear algebra calculations.”

Bell noted that the same calculation capability is required in 3D capture applications that use sensors to measure image and depth. These would include scene navigation, collision detection, occupancy sensing, driver monitoring, device control, and factory automation.

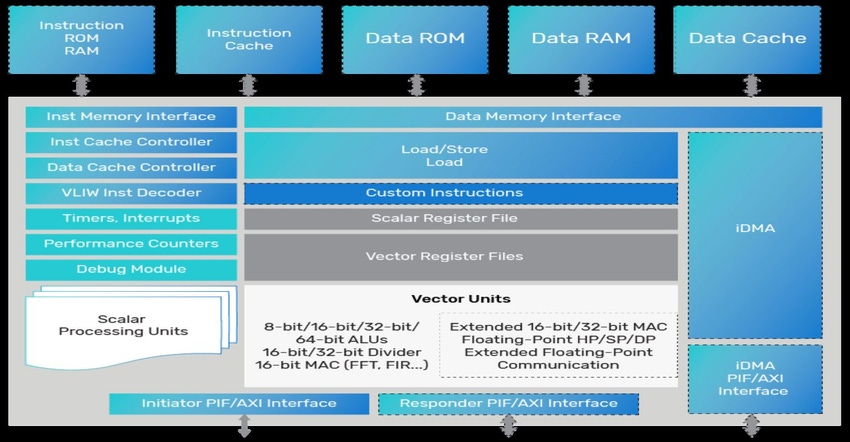

The two new cores are the ConnX 110 and ConnX 120 DSP. The ConnX 110, based on 128-bit SIMD (Single instruction, multiple data) provides support for 8-, 16-, 32-bit, 64-bit packed data. It incorporates a vectorized 16-bit and 32-bit fixed-point multiplier-accumulator with support for real and complex data. It also incorporates a vectorized 16-, 32-, and 64-bit floating-point FMA with support for real and complex data.

The more powerful ConnX 120, with 256-bit SIMD, has twice the capacity of the ConnX 110 for even-more compute-intensive calculations.

Both cores support the Tensilica Instruction Extension (TIE) language, which allows customers to tailor the instruction set, add specialized data types, and implement tightly integrated interfaces between the DSP and external logic. In addition, the new DSPs are supported by a comprehensive set of complex math library functions in the NatureDSP, Eigen and Radar libraries. All ConnX DSPs are automotive-ready with full ISO 26262 compliance to ASIL-D with FlexLock or to ASIL-B.

Both DSPs are fully ISA compatible with Cadence’s recently introduced ConnX B10 and ConnX B20 DSPs and use the same software tools and libraries across the low-end to the high-end of the company’s DSP core portfolio. According to Cadence, the DSPs are code-compatible for ease of portability for performance scalability. Clock and data gating are implemented, and logic and memory bus gating are also optional. All the DSP cores are programmable in C, thus shortening development for faster time-to-market.

Spencer Chin is a Senior Editor for Design News covering the electronics beat. He has many years of experience covering developments in components, semiconductors, subsystems, power, and other facets of electronics from both a business/supply-chain and technology perspective. He can be reached at [email protected].

About the Author(s)

You May Also Like