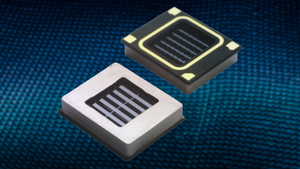

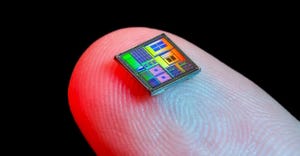

Semiconductors & Chips

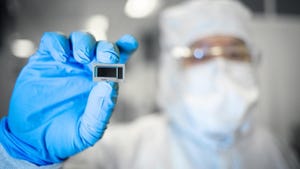

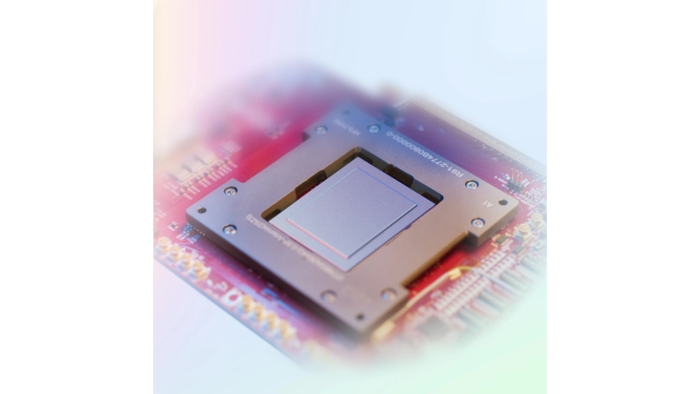

Samsung's Taylor, TX manufacturing plant.

Semiconductors & Chips

Samsung Gambles on Texas to Strengthen U.S. PresenceSamsung Gambles on Texas to Strengthen U.S. Presence

With CHIPS Act help, Korean electronics giant banks on expanded onshore plants to fend off U.S. rivals.

Sign up for the Design News Daily newsletter.

.jpg?width=300&auto=webp&quality=80&disable=upscale)